Storage hardware giant Western Digital has started pilot production of a NAND chip that manages to squeeze 512 Gigabit onto a single piece of silicon, and could considerably increase capacity and density of upcoming flash products.

WD expects to launch mass production in the second half of 2017.

“This is a great addition to our rapidly broadening 3D NAND technology portfolio. It positions us well to continue addressing the increasing demand for storage due to rapid data growth across a wide range of customer retail, mobile and data center applications,” said Dr. Siva Sivaram, executive vice president for memory technology at WD.

The company will reveal more details about the chip in a technical paper on the advancements in flash manufacturing, presented at the International Solid State Circuits Conference (ISSCC) in California.

Setting the pace

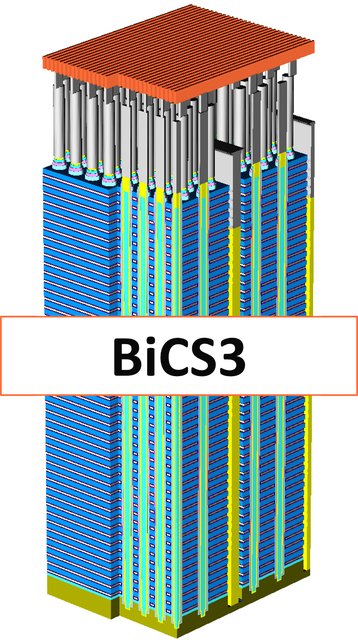

Western Digital introduced the world’s first 64-layer 3D NAND chip in July 2016. The first generation of the BiCS3 architecture was only capable of storing 256Gb, so with this latest product, the company has effectively doubled the storage capacity of its silicon.

The chip was developed in partnership with flash manufacturer Toshiba. It stores three bits per cell, across 64 layers of chemical film in a 3D NAND configuration.

WD has already launched limited manufacturing at the Toshiba plant in Yokkaichi, Japan, and is expected to scale up operations in the second half of the year, with first high capacity storage devices available shortly after.

Shipments of the products based on the company’s previous generation 3D NAND technology, BiCS2, will continue to customers in both retail and OEM.