Some of the world’s largest proponents of Reduced Instruction Set Computing (RISC) architecture in the data center have united forces to improve interoperability between RISC and the dominant x86 instruction set, backed by Intel.

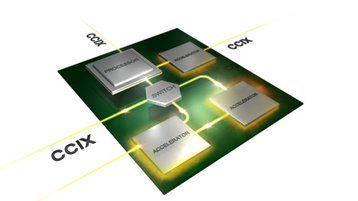

The CCIX Consortium aims develop a Cache Coherent Interconnect for Accelerators (CCIX) – technology which can enable processors with different instruction set architectures to share data with the same application acceleration engines.

So far, the Consortium includes AMD, ARM, Huawei, IBM, Mellanox, Qualcomm and Xilinx.

“A ‘one size fits all architecture’ approach to data center workloads does not deliver the required performance and efficiency,” said Lakshmi Mandyam, director of server systems and ecosystems at ARM.

“CCIX enables more optimized solutions by simplifying software development and deployment of applications that benefit from specialized processing and hardware off-load, delivering higher performance and value to data center customers.”

Sharing is caring

RISC-based chipsets typically deliver less computational power per core than a comparable x86 CPU, but they are cheaper, more energy efficient and often don’t require cooling. This category includes all processors based on designs from ARM, as well as IBM’s Power family.

In January, AMD became the latest major vendor to release an ARM-based CPU, with the launch of Opteron A1100.

These chips have small, but growing market share, and just like any CPU from Intel, they benefit from acceleration through devices like Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGAs), Digital Signal Processors (DSPs) and various coprocessors.

Some of the emerging workloads that rely on application accelerators include analytics, machine learning, NFV, wireless 4G/5G, in-memory database processing and network processing.

According to CCIX Consortium, a common acceleration framework will allow applications to access and process data irrespective of what type of system it resides on, without the need for complex programming environments.

“CCIX will leverage existing server interconnect infrastructure and deliver higher bandwidth, lower latency, and cache coherent access to shared memory,” explained Gaurav Singh, vice president of Architecture at Xilinx. “This will result in a significant improvement in the usability of accelerators and overall performance and efficiency of data center platforms.”

It is worth pointing out that neither Intel nor Nvidia have joined CCIX.