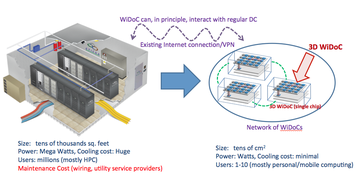

A joint project between Carnegie Mellon University and Washington State University has been awarded a National Science Foundation grant to work on a wireless Datacenter-on-a-Chip (WiDoC).

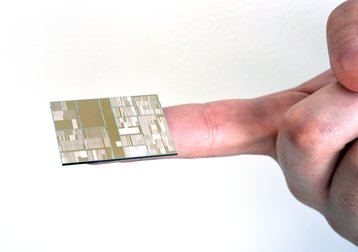

The research project aims to create a chip with thousands of cores that can run data- and compute-intensive applications ’orders of magnitude’ more efficiently than existing platforms.

A new design paradigm

The grant abstract says: “Nowadays data centers and high performance computing clusters are dominated by power, thermal, and area constraints; they occupy large spaces and necessitate sophisticated cooling mechanisms to sustain the required performance levels.

“Various big data applications like social computing, life sciences, networking, or entertainment, can benefit immensely from this new design paradigm that aims at achieving server-scale performance from hand-held devices.”

It continues: “Achieving DoC level of massive integration requires significant innovation at multiple levels of abstraction, ranging from the design of the on-chip network and associated physical layer, all the way to mapping and runtime management of various applications.”

To do this, the team have three research goals. Radu Marculescu told Phys.org: “We want to design small-world wireless architecture as a communication backbone for many core-enabled Wireless Datacenter on Chip (WiDoC), while establishing physical layer design methods for highly-integrated 3-D WiDoC suitable for low latency data communication.

“We hope to evaluate latency-power-thermal trade-offs for the proposed WiDoC platform by considering relevant big data applications.”

With $432,373 awarded so far, the team have an estimated completion date of July 31, 2019. Early results will be presented at the 2016 edition of Embedded Systems Week.